TPC Inner Sector Upgrade, FEE card development

SAMPA Chip: the New 32 Channels ASIC for the ALICE TPC and MCH Upgrades

Purpose: Design a higher density FEE cards based on the SAMPA ASIC developed for ALICE. The present FEE cards use 16 channel per-amplifier ASICS that are then digitized using semi-custom die's from ST Microelectronics (ADC's).

The new FEE called "iFEE" (used on inner sector of STAR TPC upgrade), is sometimes referred to as "HD-FEE" since this new design will have 64 channels as opposed to the current FEE cards 32 channels.

High speed readout:

The readout from the SAMPA chips is multiplexed from an FPGA (Xilinx SPARTAN 6).

The project was broken into two Design and Manufacturing processes:

FPGA (Firmware)

FPGA firmware design for production: Tonko Ljubicic, BNL

FPGA test and development firmware: Tonko Ljubicic, BNL

Circuit design (schematic) and PCB Design: Tim Camarda, BNL

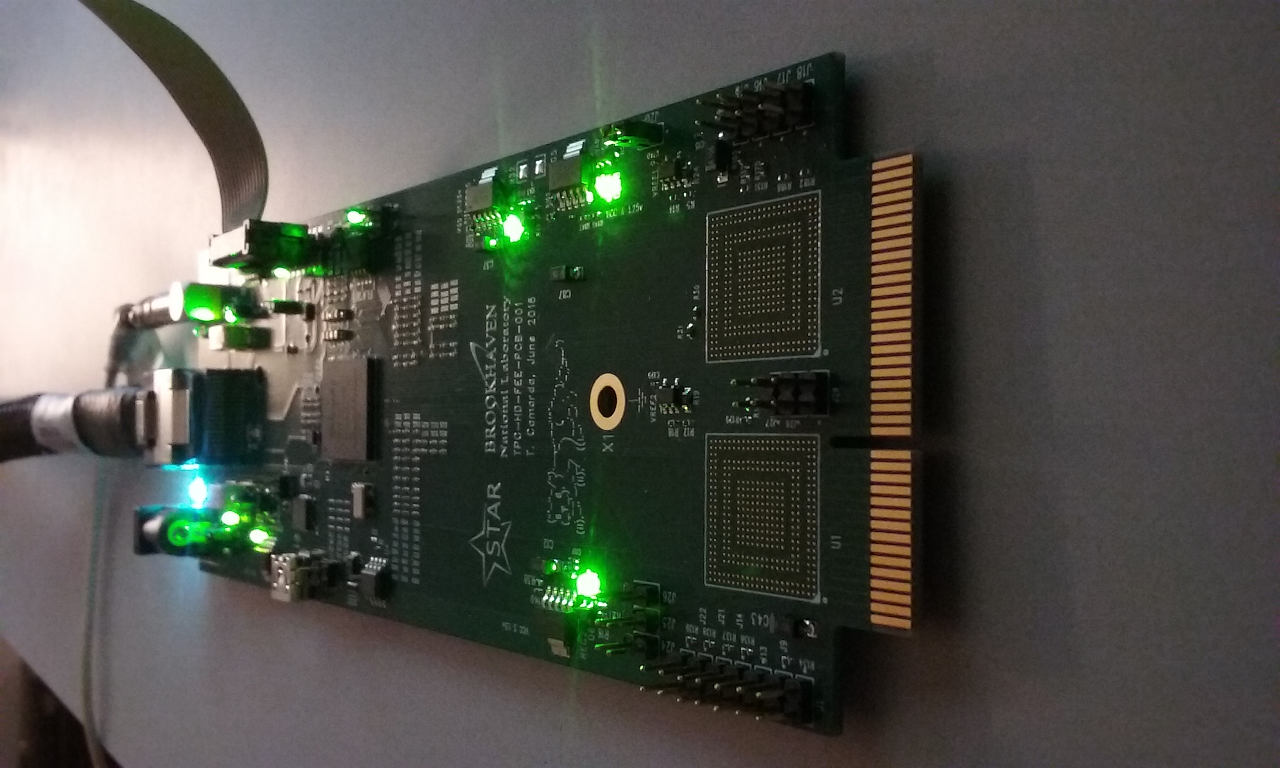

64 Channel iFEE prototype 2015

2017 Testing AKA Run 2 (2017):

- SAMPA configuration jumpers omitted. Configuration is now dynamic from FPGA control.

Power and Read-out interconnect:

The interconnection from the FEE card to the read-out cards is done through an off the shelf mini-SAS cable. The SAS cables are high speed 100ohm cables designed for use in serial ATA hard drives. The performance specifications of the cable met the requirements for the power and bandwidth for the FEE data communications link and were chosen also for reliability and cost.