ZDC (simple, i.e. RICH/RHIC) scalers in Run 2013

In Run 2013, we have changed the ZDC electronics to remove much of the NIM functionality and replace it with a custom-built, and hopefully more robust, and remotely programmable module. This is called the TCIM. Most important increase in functionality is that the "killer-bit", i.e. deadtime one can introduce, is now done internally, with a length that is remotely programmable. Also, the TCIM has internal scalers, which may eventually replace a large part of the RICH scaler setup. The deadtime is set up as non-updating, or non-paralyzable in the terminology of wikipedia (http://en.wikipedia.org/wiki/Dead_time)

Important are six signals: ZDC East, ZDC West, ZDC coincidence, with and without killer bits. As of March 15, the East and West singles with killer bits are not exported to C-AD, but the other 4 are.

There are four sources for scaler signals:

EPICS: this is the old read of the RICH scalers via epics. Done every 30 seconds, on a ring-averaged 10 reading count. The RICH actually reads every 1.4 seconds (1 second on, then 0.4 seconds dead for readout to attempt to avoid readout glitches).

Available in the usual place, onldb.starp.bnl.gov:3502, database Conditions_rich, table richScalar

MQ: This is a new readout of the RICH scalers, but via a different database route. Appears to be done every 15 seconds.

Available at onl15.starp.bnl.gov:3606, database mq_collector_Conditions_rich, table richScalar

TCIM: This is a direct readout of the internal TCIM scalers.

Available at onl15.starp.bnl.gov:3606, database mq_collector_Conditions_tcim, table tcim_registers

CAD: This is readout via the RHIC scalers, and sent back to us over cdev.

Currently grabbing it from http://online.star.bnl.gov/cdev/data/sisscaler_6a-star_*-diffm_valueandtime.dat

but it is also recorded into a database and viewable from the dbPlots.

Below "day" = seconds(/24/3600) since Midnight Dec. 31, 2012, or unix timestamp 1356930000

Currently all killer bit lengths are set to 1000 ns, but the current setting is in the TCIM database.

Mapping of signals:

| ZDC E no killer | rs13 | rich_1151E_val13 | zdc_east | sisscaler_6a_star_2 |

| ZDC W no killer | rs12 | rich_1151E_val12 | zdc_west | sisscaler_6a_star_1 |

| ZDC X no killer | rs15 | rich_1151E_val15 | zdc_coincidence | sisscaler_6a_star_3 |

| ZDC E with killer bit | rs6 | rich_1151E_val6 | zdc_east_killer | ? Not connected right now |

| ZDC W with killer bit | rs7 | rich_1151E_val7 | zdc_west_killer | ? Not connected right now |

| ZDC X with killer bit | rs8 | rich_1151E_val8 | zdc_coincidence_killer | sisscaler_6a_star_16 |

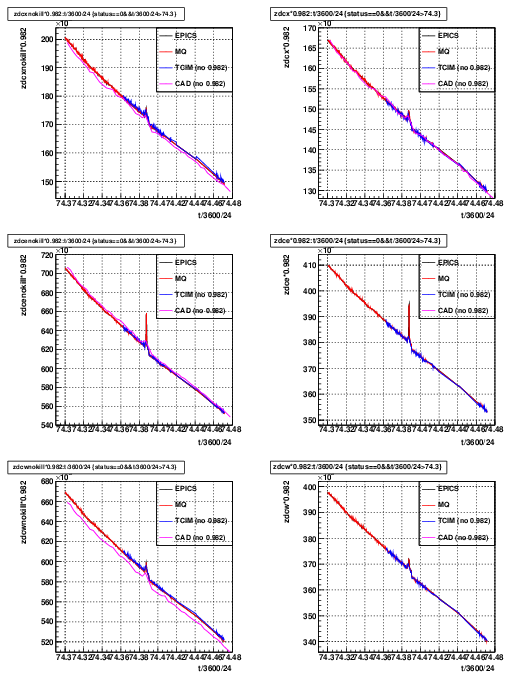

I've checked consistency between the signals below. It looks like

a) the RICH clock is slightly longer than 1 s. To be expected, since this is not a high precision counter. If I take the EPICS and MQ * 0.982 they match quite well with the TCIM scalers.

b) There is still up to a percent or so inconsistency channel by channel between the TCIM and the CAD scalers. Might be lost pulses somewhere in the chain, or noise. There is a small problem in the killer bit output of the TCIM, in that when a pulse is killed there is a very narrow low amplitude spurious pulse introduced in the output, that can be turned into a real pulse if manipulated wrong in various level conversions and optical links that need to be done to get the signal to CAD. But this is currently suppressed by a delayed veto in the DAQ room for the signal ZDCX with killer bit.

In terms of checking the killer bit logic, the correction factor should be

real = killed/(1.-killed*deadtime[s]). Below shows the result for MQ, TCIM, and RHIC (for the signal where I can check). Looks to be good to the percent level or so. Probably some issues in the assumption for the above formula that the pulses are uniformly spread in time.

.png)

As an FYI, since this information does not appear to be easily accessible, here is the mapping of the C-AD scaler bits.

Note that the hardware inputs and what is available via CDEV is rotated by 1. This is a copy of what is written in the control room.

| Hardware | CDEV software (sisscaler_*) | Meaning |

| 1 | 16 | ZDC Coincidence with killer bit |

| 2 | 1 | ZDC West without killer bit |

| 3 | 2 | ZDC East without killer bit |

| 4 | 3 | ZDC Coincidence without killer bit |

| 5 | 4 | BBC Lumi . Y+ . B+ |

| 6 | 5 | ZDC West with killer bit |

| 7 | 6 | ZDC East with killer bit |

| 8 | 7 | VT201 bit from Hank |

| 9 | 8 | Blue_back.Yellow_abort |

| 10 | 9 | BBC Lumi .Y- . B+ |

| 11 | 10 | Yellow_back.Blue_abort |

| 12 | 11 | BBC E.W 20 ns overlap (BBC lumi) |

| 13 | 12 | BBC E |

| 14 | 13 | BBC W |

| 15 | 14 | BBC E.W (E delayed -> Blue Background) |

| 16 | 15 | BBC E.W (W delayed -> Yellow Background) |

- dunlop's blog

- Login or register to post comments