Vped Confusion - 2018 Part II

Forget everything below the line. The issue seems to be EQ1. ARGH!!!

Ok, the plots are at:

In small size for Mike : drupal.star.bnl.gov/STAR/system/files/Compare_small_vped02152018.pdf

In big size to be able to read: drupal.star.bnl.gov/STAR/system/files/Compare_big_vped02152018.pdf

Note: This are pedestal rhic clock clean files, taken over 2 days (so some drift could happen). Also, only about 500 channels were cabled up, so some channels were blank.

The crate that was *not* cabled was EQ1, which is the one we're not seeing signals for. Now, I thought that some of it was cabled, but I will have to confirm.

*****************************************

Currently we are trying to understand why changing vped (which should control the DC offset, and can be an integer between -128 and 128) does not seem to shift the pedestals that we measure in the EPD electronics. I posted my first scattered thought at:

drupal.star.bnl.gov/STAR/blog/rjreed/vped-confusion-2018

I have learned several things. One is that the pedestal subtraction is applied in pedAsPhys runs, which can confuse things. However, the difference should be seen in simple rhic clock clean pedestal runs.

From the previous blog, I compared several different runs and noticed some very odd behavior.

I set the vped to -90 in every channel and took a pedestal rhic-clock clean. (run 19044047) Then we took several pedAsPhy runs

19044048 - vped -90. This should be the default, I would expect all of the values to be around 0.

19044049 - vped - ch0 to +90 . This run I had meant to only turn those channels hooked up to a QT ch 0 to 90 and leave the rest at -90. Unfortunately, I actually changed the other channels back to my default of 20.

19044050 - vped - ch1 to +90 - Same as 049 but instead of QT ch 0, I changed QT ch 1.

The total summary of every channel can be found at: drupal.star.bnl.gov/STAR/system/files/Compare_19044048to50.pdf

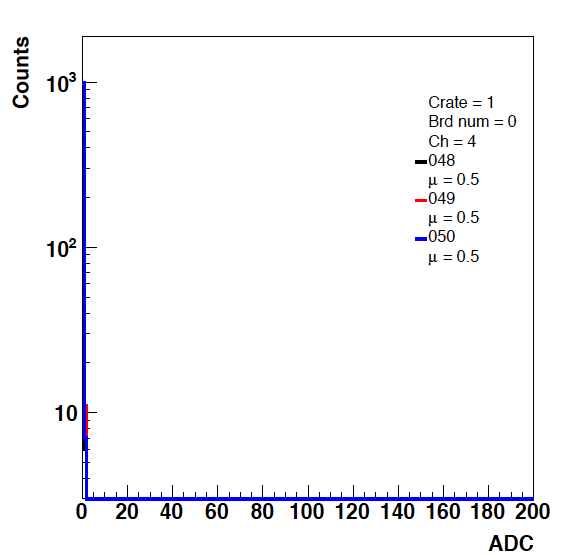

Figure 1: QT32B ADC channel from the 3 pedAsPhys runs. All QT32B channels looked like this, even Ch0 and Ch1 channels, which should show some change. It was not a case of mismapping the channels, as no other channel showed a signal in it.

Then in the QT32C boards, the story got even stranger:

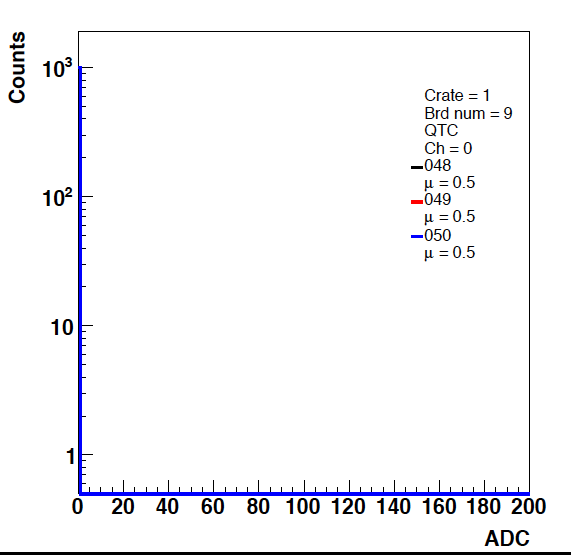

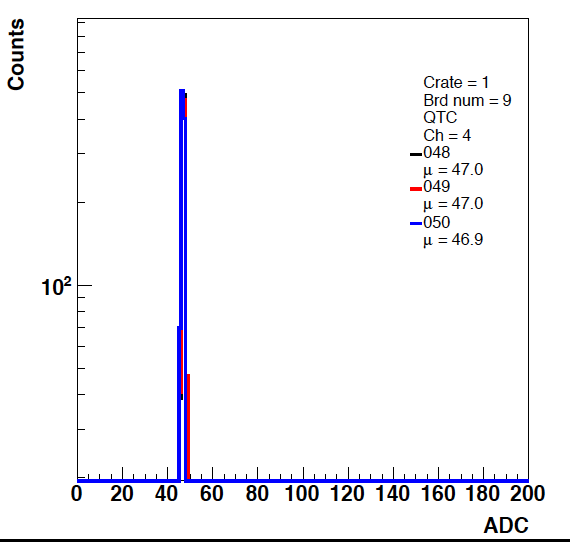

Figure 2: QT32C board. On the left is an ADC channel, which looked similar to the QT32Bs. The plot on the right showed a TAC channel, which I am not entirely sure I understand why there was a difference here, other than the fact that for these channels the pedestals are precisely 0.

Even more confusing is that the other ADC channels in some of the QT32C boards show the same effect as the plot on the right of Figure 2.

There were two questions here, one is that the range of -90 to 90 for vped might have been too large, and the effect of the pedestal subtraction so I then looked directly at pedestal runs.

The summary of this study can be seen at: drupal.star.bnl.gov/STAR/system/files/Pedestal_19045001vs002vs003vs005_small.pdf

The rhic-clock -clean pedestal runs that we took are:

19045 001 - vped = 20 (default)

002 vped = 0

003 vped = -20

004 vped = -90

005 vped = 90

006 vped = 20

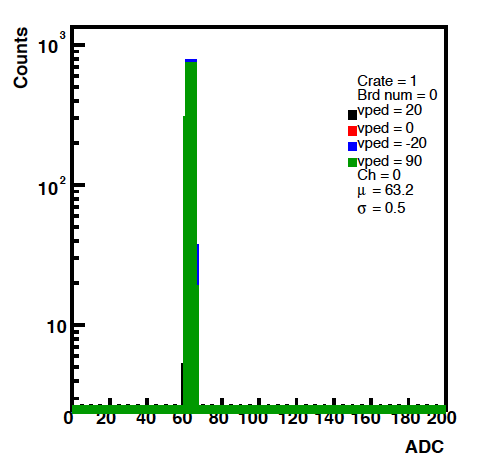

Figure 3: An example of different vped settings for a QT32B board.

In figure 3, we see that none of the pedestals changed at all for the QT32B boards, and this is true of all channels. This is consistent of what we saw in the pedAsPhys runs, but at least we can see the pedestals themselves.

Figure 4: Results for a QT32C board.

I do not understand Figure 4 at all. The first row and the 3rd row are ADC channels, the 2nd and 4th are TAC. Why are things only changing in the 3rd row? I changed the vped value for every channel. Why were we seeing the changes in the tac channels in the pedAsPhys runs.

It was obvious that we weren't sure what we were doing, so we did two other tests today.

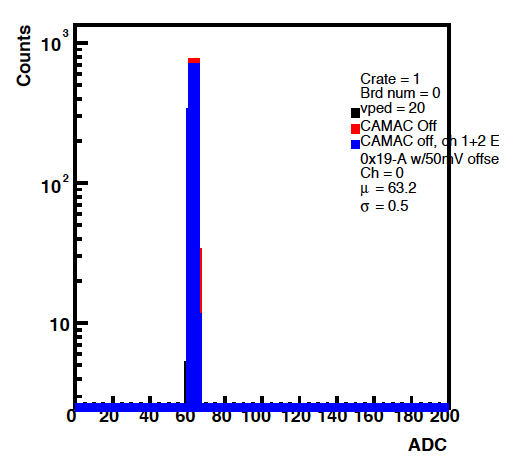

19046002 - CAMAC off, everything plugged in normally with no offset

19046003 - CAMAC off, channels 1+2 from EQ1-0x19-A with a 50mV offset

EQ1-0x19 is a QT 32C

The summary is at: drupal.star.bnl.gov/STAR/system/files/PedChangeCamacOff50mv_02152018.pdf

I have also included a run from yesterday with the CAMAC on and at our default vped of 20.

Figure 5: QT32B, default vped, CAMAC off and 50 mV into a QT32C board.

Figure 5 indicates a definite issue, and all QT32B cards within this crate are the same, where the pedestal is identical for each channel with the CAMAC on or off. Given the spread last year, this is non-physical. Maybe the B boards aren't being read in somehow? There is movement on the Cs but not the Bs.

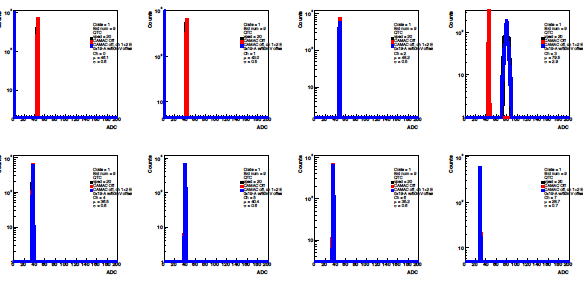

Figure 6: QT32C board. Upper left 2 panels are the channels that had the 50 mV in it.

In Figure 6, we see the effect of the board that had the 50 mV put into channel 1 and channel 2. We see that this made the pedestal very negative. What is also very strange is the upper right. I honestly don't know what is up between the red and blue curves, as everything in this channel should be identical.

- rjreed's blog

- Login or register to post comments