Holes in EPD QA plots

Updated on Mon, 2020-01-13 15:57. Originally created by adams92 on 2019-12-16 13:17.

In run 19, we were seeing that, over the course of a few hours, the <ADC> displayed in the QA plots for some of the tiles would slowly become blue.

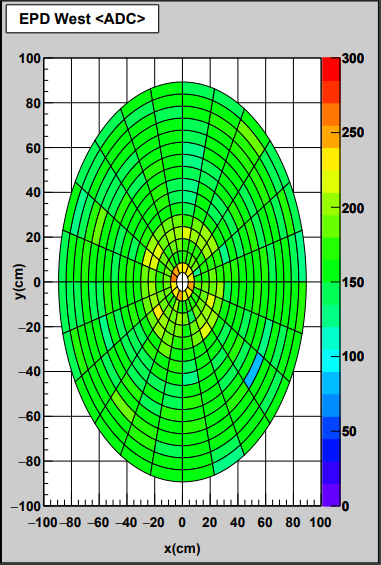

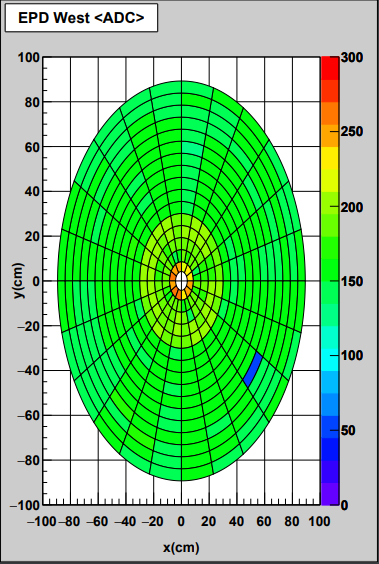

Figure 1: Run 20081007, where a tile is slightly blue

Figure 1: Run 20081007, where a tile is slightly blue

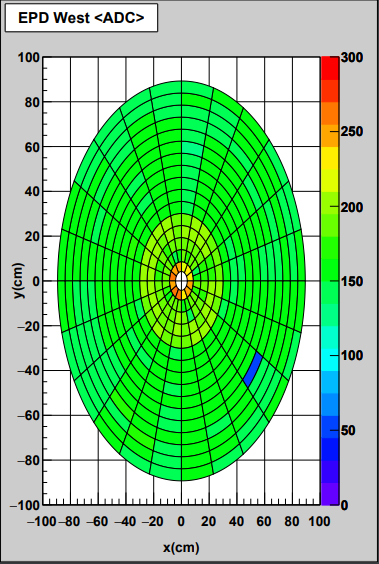

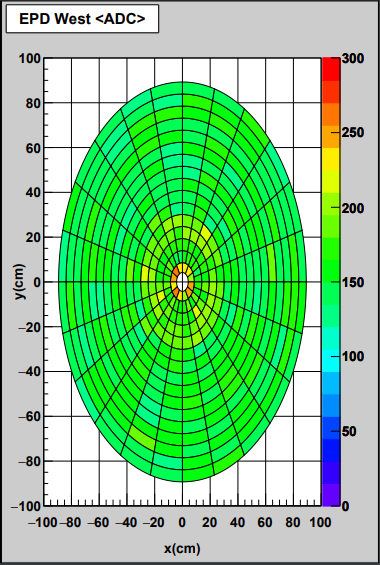

Figure 2: Run 20081009, where a tile is noticeably blue

Figure 2: Run 20081009, where a tile is noticeably blue

We also noticed that, after a pedestal run, the <ADC> for these tiles became normal.

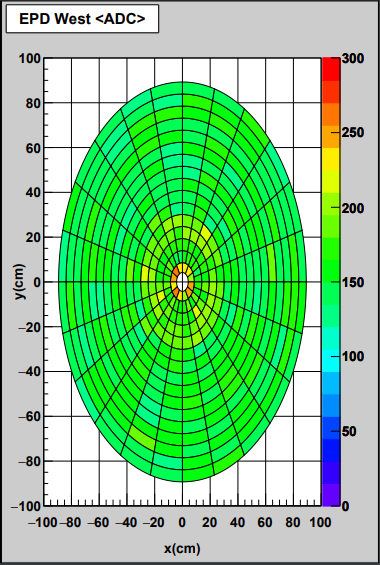

Figure 3: Run 20081025, where the blue tile has a normal <ADC>

Figure 3: Run 20081025, where the blue tile has a normal <ADC>

A nice study by Rosi showed that there were still MIP peaks in the ADC distributions that looked fine, but they were shifted to higher ADC values and their pedestals were huge. Rosi concluded that this was due to a trigger algorithm change, and since the trigger algorithm was reverted there was nothing that was needed to be done.

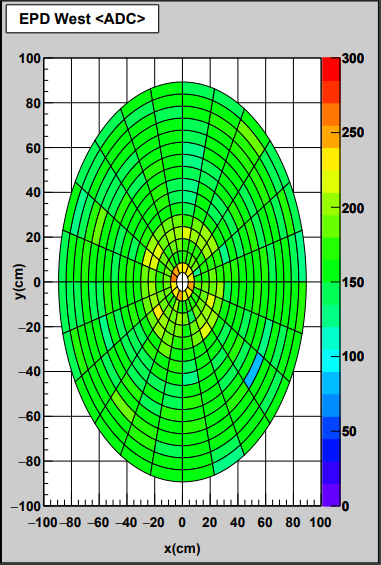

In run 20, around run 20348027, we started seeing this issue pop up again.

The decision was ultimately to change a QT32B daughter board. See this study by Rosi.

Figure 1: Run 20081007, where a tile is slightly blue

Figure 1: Run 20081007, where a tile is slightly blue Figure 2: Run 20081009, where a tile is noticeably blue

Figure 2: Run 20081009, where a tile is noticeably blueWe also noticed that, after a pedestal run, the <ADC> for these tiles became normal.

Figure 3: Run 20081025, where the blue tile has a normal <ADC>

Figure 3: Run 20081025, where the blue tile has a normal <ADC> A nice study by Rosi showed that there were still MIP peaks in the ADC distributions that looked fine, but they were shifted to higher ADC values and their pedestals were huge. Rosi concluded that this was due to a trigger algorithm change, and since the trigger algorithm was reverted there was nothing that was needed to be done.

In run 20, around run 20348027, we started seeing this issue pop up again.

The decision was ultimately to change a QT32B daughter board. See this study by Rosi.

»

- adams92's blog

- Login or register to post comments